- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

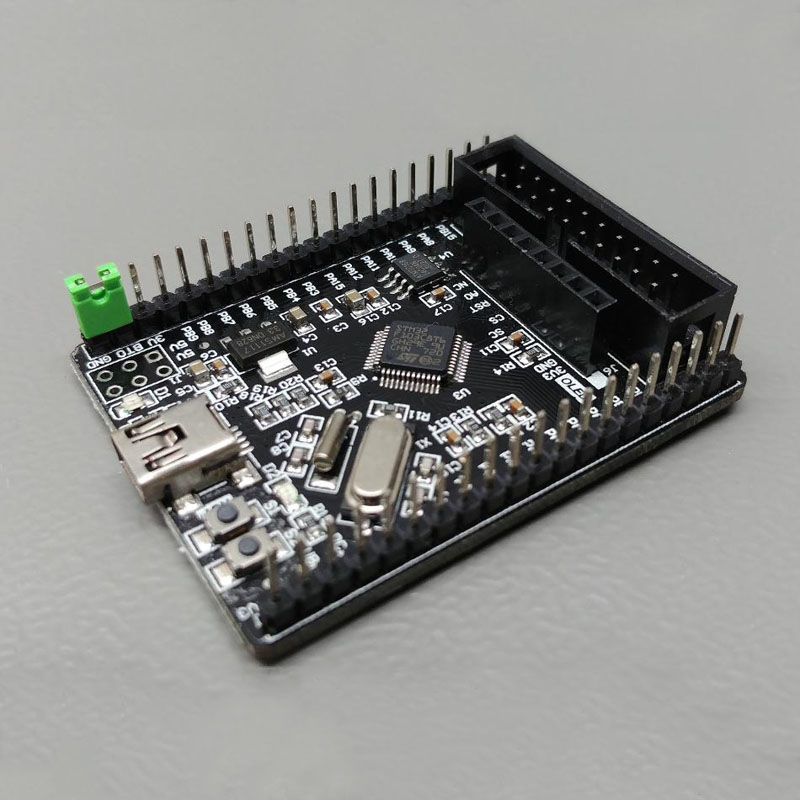

ARM STM32 MCU-Board

Ningbo Hi-tech Easy Choice Technology Co., Ltd ist ein Hightech-Unternehmen, das sich mit dem Design, der Entwicklung und der Produktion des ARM STM32 MCU Boards beschäftigt. Der Ruf unseres Unternehmens basiert auf guter Bonität und außergewöhnlichem Service, was zu langfristigen Kooperationen mit bedeutenden Unternehmen, Regierungsbehörden und einer breiten Benutzergemeinschaft geführt hat. Wir sind auf die Entwicklung intelligenter elektronischer Steuerplatinen, das Design mechanischer und elektrischer Steuerungsprodukte spezialisiert. Entwicklung von Einzelchip-Mikrocomputern, Schaltungsdesign und Postproduktionstests. Wir können den Steuerschaltkreis individuell an Ihre Bedürfnisse anpassen und so die Erfüllung Ihrer beabsichtigten Produktfunktionalitäten ermöglichen, unabhängig davon, ob Sie explizite Funktionsanforderungen oder lediglich eine Idee liefern.

Anfrage absenden

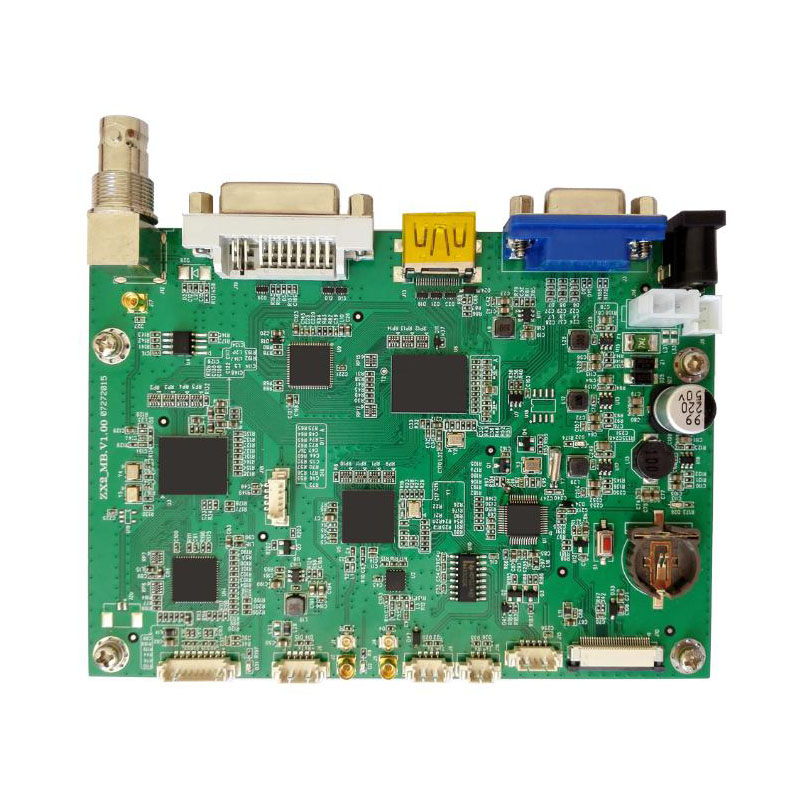

Die Entwicklung von Steuerplatinen für Industrieprodukte von YCTECH umfasst Softwaredesign für Industriesteuerplatinen, Software-Upgrades, Schaltplandesign, PCB-Design, PCB-Produktion und PCBA-Verarbeitung an der Ostküste Chinas. Unser Unternehmen entwirft, entwickelt und produziert ARM STM32 MCU-Boards. Kern: ARM32-Bit-Cortex-M3-CPU, die höchste Betriebsfrequenz beträgt 72 MHz, 1,25 DMIPS/MHz. Einzelzyklus-Multiplikation und Hardware-Division.

Speicher: On-Chip integrierter 32–512 KB Flash-Speicher. 6–64 KB SRAM-Speicher.

Takt-, Reset- und Energieverwaltung: 2,0–3,6 V Stromversorgung und Antriebsspannung für die I/O-Schnittstelle. Power-On-Reset (POR), Power-Down-Reset (PDR) und programmierbarer Spannungsdetektor (PVD). 4–16 MHz Quarzoszillator. Eingebauter 8-MHz-RC-Oszillatorschaltkreis, der vor dem Werk eingestellt wurde. Interner 40-kHz-RC-Oszillatorschaltkreis. PLL für CPU-Takt. 32-kHz-Quarz mit Kalibrierung für RTC.

Geringer Stromverbrauch: 3 Modi mit geringem Stromverbrauch: Schlaf-, Stopp- und Standby-Modus. VBAT zur Stromversorgung der RTC- und Backup-Register.

Debug-Modus: serielles Debug (SWD) und JTAG-Schnittstelle.

DMA: 12-Kanal-DMA-Controller. Unterstützte Peripheriegeräte: Timer, ADC, DAC, SPI, IIC und UART.

Drei 12-Bit-A/D-Wandler auf US-Ebene (16 Kanäle): A/D-Messbereich: 0–3,6 V. Duale Sample-and-Hold-Funktion. Auf dem Chip ist ein Temperatursensor integriert.

2-Kanal-12-Bit-D/A-Wandler: STM32F103xC, STM32F103xD, STM32F103xE exklusiv.

Bis zu 112 schnelle I/O-Ports: Je nach Modell gibt es 26, 37, 51, 80 und 112 I/O-Ports, die alle 16 externen Interrupt-Vektoren zugeordnet werden können. Alle außer den analogen Eingängen können Eingänge bis zu 5 V akzeptieren.

Bis zu 11 Timer: 4 16-Bit-Timer mit jeweils 4 IC/OC/PWM oder Impulszählern. Zwei erweiterte 16-Bit-6-Kanal-Steuerungstimer: Bis zu 6 Kanäle können für die PWM-Ausgabe verwendet werden. 2 Watchdog-Timer (unabhängiger Watchdog und Fenster-Watchdog). Systick-Timer: 24-Bit-Abwärtszähler. Zur Ansteuerung des DAC werden zwei 16-Bit-Basis-Timer verwendet.

Bis zu 13 Kommunikationsschnittstellen: 2 IIC-Schnittstellen (SMBus/PMBus). 5 USART-Schnittstellen (ISO7816-Schnittstelle, LIN, IrDA-kompatibel, Debug-Steuerung). 3 SPI-Schnittstellen (18 Mbit/s), davon zwei mit IIS gemultiplext. CAN-Schnittstelle (2.0B). USB 2.0-Full-Speed-Schnittstelle. SDIO-Schnittstelle.

ECOPACK-Paket: Mikrocontroller der Serie STM32F103xx verwenden das ECOPACK-Paket.

Systemeffekt

1. ARM Cortex-M3-Kern integriert mit integriertem Flash- und SRAM-Speicher. Im Vergleich zu 8/16-Bit-Geräten bietet der ARM Cortex-M3 32-Bit-RISC-Prozessor eine höhere Codeeffizienz. STM32F103xx-Mikrocontroller verfügen über einen eingebetteten ARM-Kern und sind daher mit allen ARM-Tools und -Software kompatibel.

2. Eingebetteter Flash-Speicher und RAM-Speicher: Integrierter bis zu 512 KB großer eingebetteter Flash, der zum Speichern von Programmen und Daten verwendet werden kann. Bis zu 64 KB eingebetteter SRAM können mit CPU-Taktgeschwindigkeit gelesen und geschrieben werden (keine Wartezustände).

3. Variabler statischer Speicher (FSMC): FSMC ist in STM32F103xC, STM32F103xD, STM32F103xE eingebettet, mit 4 Chipauswahlen und unterstützt vier Modi: Flash, RAM, PSRAM, NOR und NAND. 3 FSMC-Interrupt-Leitungen sind nach OR mit NVIC verbunden. Es gibt kein Lese-/Schreib-FIFO, außer bei PCCARD, Codes werden aus dem externen Speicher ausgeführt, Boot wird nicht unterstützt und die Zielfrequenz ist gleich SYSCLK/2. Wenn der Systemtakt also 72 MHz beträgt, erfolgt der externe Zugriff mit 36 MHz.

4. Nested Vectored Interrupt Controller (NVIC): Er kann 43 maskierbare Interrupt-Kanäle (mit Ausnahme der 16 Interrupt-Leitungen von Cortex-M3) verarbeiten und bietet 16 Interrupt-Prioritäten. Eng gekoppelter NVIC erreicht eine geringere Interrupt-Verarbeitungslatenz, überträgt die Adresse der Interrupt-Eintragsvektortabelle direkt an den Kernel, eng gekoppelte NVIC-Kernelschnittstelle, ermöglicht die Vorverarbeitung von Interrupts, verarbeitet später eintreffende Interrupts mit höherer Priorität und unterstützt Tail Chain, automatische Speicherung der Prozessorstatus, und der Interrupt-Eintrag wird automatisch wiederhergestellt, wenn der Interrupt beendet wird, ohne dass ein Befehl eingreifen muss.

5. Externer Interrupt-/Event-Controller (EXTI): Der externe Interrupt-/Event-Controller besteht aus 19 Kantendetektorlinien zur Generierung von Interrupt-/Event-Anfragen. Jede Zeile kann individuell zur Auswahl des Triggerereignisses (steigende Flanke, fallende Flanke oder beides) konfiguriert und individuell maskiert werden. Es gibt ein ausstehendes Register, um den Status von Interrupt-Anforderungen aufrechtzuerhalten. EXTI kann erkennen, wenn ein Impuls auf der externen Leitung länger als die Periode des internen APB2-Takts ist. Bis zu 112 GPIOs sind an 16 externe Interrupt-Leitungen angeschlossen.

6. Takt und Start: Beim Starten muss weiterhin der Systemtakt ausgewählt werden, beim Zurücksetzen wird jedoch der interne 8-MHz-Quarzoszillator als CPU-Takt ausgewählt. Ein externer 4-16MHz-Takt kann ausgewählt werden und wird auf Erfolg überwacht. Während dieser Zeit ist der Controller deaktiviert und die Software-Interrupt-Verwaltung wird anschließend deaktiviert. Gleichzeitig steht bei Bedarf (z. B. bei Ausfall eines indirekt genutzten Quarzoszillators) das Interrupt-Management des PLL-Takts voll zur Verfügung. Zur Konfiguration der AHB-Frequenz können mehrere Vorkomparatoren verwendet werden, darunter Hochgeschwindigkeits-APB (PB2) und Niedriggeschwindigkeits-APB (APB1). Die höchste Frequenz des Hochgeschwindigkeits-APB beträgt 72 MHz und die höchste Frequenz des Niedriggeschwindigkeits-APB beträgt 36 MHz.

7. Boot-Modus: Beim Start wird der Boot-Pin verwendet, um eine der drei Boot-Optionen auszuwählen: Import aus Benutzer-Flash, Import aus Systemspeicher und Import aus SRAM. Das Boot-Importprogramm befindet sich im Systemspeicher und wird zum Neuprogrammieren des Flash-Speichers über USART1 verwendet.

8. Stromversorgungsschema: VDD, der Spannungsbereich beträgt 2,0 V–3,6 V, die externe Stromversorgung erfolgt über den VDD-Pin, der für I/O und internen Spannungsregler verwendet wird. VSSA und VDDA, der Spannungsbereich beträgt 2,0–3,6 V, externer analoger Spannungseingang für ADC, Reset-Modul, RC und PLL, innerhalb des Bereichs von VDD (ADC ist auf 2,4 V begrenzt), VSSA und VDDA müssen entsprechend an VSS angeschlossen werden und VDD. VBAT, der Spannungsbereich beträgt 1,8–3,6 V. Wenn VDD ungültig ist, liefert es Strom für RTC, externen 32-kHz-Quarzoszillator und Backup-Register (realisiert durch Leistungsumschaltung).

9. Energieverwaltung: Das Gerät verfügt über eine vollständige Power-On-Reset- (POR) und Power-Down-Reset- (PDR) Schaltung. Diese Schaltung ist immer wirksam, um sicherzustellen, dass einige notwendige Vorgänge ausgeführt werden, wenn von 2 V gestartet wird oder auf 2 V abfällt. Wenn VDD unter einem bestimmten unteren Grenzwert VPOR/PDR liegt, kann das Gerät auch ohne externe Reset-Schaltung im Reset-Modus bleiben. Das Gerät verfügt über einen eingebetteten programmierbaren Spannungsdetektor (PVD). Der PVD wird verwendet, um VDD zu erkennen und mit dem VPVD-Grenzwert zu vergleichen. Ein Interrupt wird generiert, wenn VDD kleiner als VPVD oder VDD größer als VPVD ist. Die Interrupt-Serviceroutine kann eine Warnmeldung generieren oder die MCU in einen sicheren Zustand versetzen. PVD wird per Software aktiviert.

10. Spannungsregelung: Der Spannungsregler verfügt über 3 Betriebsmodi: Hauptbetrieb (MR), geringer Stromverbrauch (LPR) und Abschaltung. MR wird im herkömmlichen Sinne im Regelmodus (Laufmodus) verwendet, LPR wird im Stoppmodus verwendet und Power-Down wird im Standby-Modus verwendet: Der Spannungsreglerausgang ist hochohmig, der Kernkreis wird heruntergefahren, einschließlich Nullverbrauch (der Inhalt der Register und des SRAM geht nicht verloren).

11. Modus mit geringem Stromverbrauch: STM32F103xx unterstützt drei Modi mit geringem Stromverbrauch, um die beste Balance zwischen geringem Stromverbrauch, kurzer Startzeit und verfügbaren Weckquellen zu erreichen. Schlafmodus: Nur die CPU hört auf zu arbeiten, alle Peripheriegeräte laufen weiter, wecken die CPU auf, wenn ein Interrupt/Ereignis auftritt; Stoppmodus: Ermöglicht die Aufrechterhaltung des Inhalts von SRAM und Registern bei minimalem Stromverbrauch. Die Takte im 1,8-V-Bereich werden alle gestoppt, die PLL-, HSI- und HSE-RC-Oszillatoren werden deaktiviert und der Spannungsregler wird in den Normal- oder Energiesparmodus versetzt. Das Gerät kann über eine externe Interrupt-Leitung aus dem Stopp-Modus aufgeweckt werden. Die externe Interrupt-Quelle kann eine von 16 externen Interrupt-Leitungen, ein PVD-Ausgang oder eine TRC-Warnung sein. Standby-Modus: Um den geringsten Stromverbrauch zu erzielen, wird der interne Spannungsregler ausgeschaltet, sodass der 1,8-V-Bereich ausgeschaltet ist. PLL-, HSI- und HSE-RC-Oszillatoren sind ebenfalls deaktiviert. Nach dem Eintritt in den Standby-Modus gehen neben den Backup-Registern und Standby-Schaltkreisen auch die Inhalte von SRAM und Registern verloren. Das Gerät verlässt den Standby-Modus, wenn ein externer Reset (NRST-Pin), ein IWDG-Reset, eine steigende Flanke am WKUP-Pin oder eine TRC-Warnung auftritt. Beim Wechsel in den Stopp- oder Standby-Modus werden TRC, IWDG und zugehörige Taktquellen nicht gestoppt.